ON Semiconductor®

www.onsemi.com

# Advance Information

#### **Bi-CMOS IC**

# 9-channel LED Driver

#### Overview

The LV5237JA is a 9-channel LED driver IC that is capable of switching between constant-current output and open drain output. Peak output current is IO max=100mA. It enables 2-wire/3-wire serial bus control (address designation) to be set arbitrarily using an external pin. Also possible are 9-channel LED ON/OFF control and the setting of the PWM luminance in

Up to 81 driver ICs can be connected using the slave address setting pins.

SSOP24 (225mil)

#### **Function**

- 9-channel output constant-current LED driver/open drain output LED driver (selected by using an external pin) Supports separate ON/OFF setting for each LED output, high withstand voltage (VOUT<42V)

- In the constant-current mode (OUTSCT: L), the reference current is set by the value of resistor connected to the external pin (RT1).

Built-in D/A (5 bits) for switching current level

... 0.86mA to 31.24mA (RGB drive)

Constant current (IO max=100mA) for full-color

LEDs × 9 channels

• In the open drain mode (OUTSCT: H), high current drive

(IO max=100mA) × 9 channels

• In the constant-current mode (OUTSCT: M)

Only RGB3 is open drain (IO max=100mA)

- Luminance adjustment using internal PWM control (256 steps), It copes with independent PWM control for each LED output

- · 8-bit PWM luminance dimming (0% to 99.6%)

- 3-phase PWM

- Selection of 2-wire/ 3-wire serial bus control signals enabled (switching using an external pin)

- Schmitt trigger input (3.3V/5V)

- Slave addressing (4 bits, connection of up to 81 driver ICs possible)

- Input Power supply supports 12V

- Internal reference output terminal (5V)

- Low current consumption

- Output malfunction protection circuits (thermal protection function, UVLO detection protection function, Power on RESET)

This document contains information on a new product. Specifications and information herein are subject to change without notice.

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 23 of this data sheet.

## **Specifications**

**Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol              | Conditions  | Ratings     | Unit |

|-----------------------------|---------------------|-------------|-------------|------|

|                             | V <sub>CC</sub> max |             | 13.6        | V    |

| Maximum supply voltage      | VLED                | VLED        | 42          | V    |

|                             | VREF                | VREF        | 5.8         | V    |

| Output voltage              | V <sub>O</sub> max  | LED off     | 42          | V    |

| Output current              | I <sub>O</sub> max  | Open drain  | 100         | mA   |

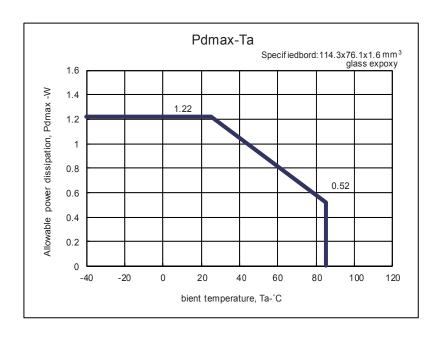

| Allowable power dissipation | Pd max              | Ta ≤ 25°C * | 1.22        | W    |

| Operating temperature       | Topr                |             | -25 to +85  | °C   |

| Storage temperature         | Tstg                |             | -40 to +150 | °C   |

<sup>\*</sup> Specified board: 114.3mm × 76.1mm × 1.6mm, glass epoxy board. Exposed Die-pad area is not a substrate mounting. [Warning]: If you should intend to use this IC continuously under high temperature, high current, high voltage, or drastic temperature change, even if it is used

within the range of absolute maximum ratings or operating conditions, there is a possibility of decrease reliability. Please contact us for a confirmation.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **Recommended Operating Conditions** at Ta = 25°C

| Parameter                      | Symbol              | Conditions       | Ratings     | Unit |

|--------------------------------|---------------------|------------------|-------------|------|

|                                | V <sub>CC</sub> op  | sv <sub>CC</sub> | 3.1 to 12.8 | V    |

| Operating supply voltage range | V <sub>LED</sub> op | V <sub>LED</sub> | 3.1 to 42   | V    |

|                                | V <sub>REF</sub> op | V <sub>REF</sub> | 3.1 to 5.5  | ٧    |

[Warning]: The VLED terminal becomes the terminal for protection of the LED drive output. Please be connected to the power supply same as LED drive. When IC power supply (SVCC) and power supply of the LED or two kinds of power supply is more than it, please connect VLED to the highest potential and the power supply that it is

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 5V$ (=VREF)

| Devenuetes                          | Courselle and     | Condition -                                                       |       | Ratings |       | Unit |

|-------------------------------------|-------------------|-------------------------------------------------------------------|-------|---------|-------|------|

| Parameter                           | Symbol            | Conditions                                                        | min   | max     | Offic |      |

| Consumption current                 | I <sub>CC</sub> 1 | LED off                                                           | 1.0   | 1.8     | 2.9   | mA   |

| Reference current pin voltage       | VRT               | RT1=20kΩ                                                          | 1.14  | 1.22    | 1.30  | V    |

| MAX output current                  | ΔIL               | V <sub>O</sub> =0.7 to 4.0V(Same channel line regulation)         | -10   |         |       | %    |

| Between bits output current         | Δl <sub>O</sub> L | I <sub>O</sub> =31.24mA<br>(Between bits pairing characteristics) |       |         | 5     | %    |

| Maximum LED driver output current 1 | IMAX1             | RT1=20kΩ<br>LED OUTSCT= L                                         | 29.36 | 31.24   | 33.12 | mA   |

| LED output on resistance 1          | Ron1              | I <sub>O</sub> = 10mA                                             |       | 10      | 20    | Ω    |

| OFF leak current                    | lleak             | LED OFF                                                           |       |         | 10    | μА   |

| Power on RESET voltage              | VPOR              | The voltage that is canceled                                      |       | 2.5     |       | V    |

| Reset voltage                       | VRST              | UVLO voltage                                                      |       | 2.3     |       | V    |

| VREF voltage                        | VREF              | VREF=open                                                         |       | 4.9     |       | V    |

| VREF voltage                        | VREF1             | V <sub>CC</sub> = 6.0V, I <sub>O</sub> = 10mA                     | 4.7   | 5.1     | 5.4   | V    |

| Oscillator frequency                | Fosc              |                                                                   |       | 1000    |       | kHz  |

<sup>\*</sup>Power on RESET

Reset all the data in the IC at the time of power activation. And it becomes the default setting.

When SVCC decreases, it turns off LED output terminal.

When a temperature in the IC rises, it turns off output terminal. When temperature falls, it returns by oneself.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>\*</sup>UVLO detection protection function

<sup>\*</sup> Thermal protection function

# Control circuit at Ta = 25°C, $V_{CC} = 5.0V$ (=VREF)

| Descriptor | O. make al | Candidan                        |      | Ratings |       | Unit |

|------------|------------|---------------------------------|------|---------|-------|------|

| Parameter  | Symbol     | Conditions                      | min  | max     | Offic |      |

| H level 1  | VH1        | Input H level OUTSCT            | 4.5  |         | 5.0   | ٧    |

| M level 1  | VM1        | Input M level OUTSCT            | 1.8  |         | 3.0   | ٧    |

| L level 1  | VL1        | Input L level OUTSCT            | -0.2 |         | 0.5   | V    |

| H level 2  | VH2        | Input H level CTLSCT            | 3.5  |         | 5.0   | ٧    |

| L level 2  | VL2        | Input L level CTLSCT            | -0.2 |         | 0.5   | V    |

| H level 3  | VH3        | Input H level SCLK, SDATA, SDEN | 4.0  |         | 5.0   | ٧    |

| L level 3  | VL3        | Input L level SCLK, SDATA, SDEN | -0.2 |         | 1.0   | ٧    |

| H level 4  | VH4        | Input H level A0 to A3          | 4.5  |         | 5.0   | V    |

| M level 4  | VM4        | Input H level A0 to A3          | 1.8  |         | 3.0   | ٧    |

| L level 4  | VL4        | Input L level A0 to A3          | -0.2 |         | 0.5   | ٧    |

# **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 3.3V$ (=VREF)

| Danamatan                           | O: mak al         | Conditions                                                     |      | Ratings |      | Unit |

|-------------------------------------|-------------------|----------------------------------------------------------------|------|---------|------|------|

| Parameter                           | Symbol            | Conditions                                                     | min  | typ     | max  | Unit |

| Consumption current                 | I <sub>CC</sub> 2 | LED off                                                        |      | 1.6     |      | mA   |

| Reference current pin voltage       | VRT               | RT1=20kΩ                                                       | 1.14 | 1.22    | 1.30 | V    |

| MAX output current                  | ΔIL               | V <sub>O</sub> =0.7 to 4.0V(Same channel line regulation)      | -10  |         |      | %    |

| Between bits output current         | Δl <sub>O</sub> L | I <sub>O</sub> =31.24mA (Between bits pairing characteristics) |      |         | 5    | %    |

| Maximum LED driver output current 1 | IMAX1             | RT1=20kΩ<br>LED OUTSCT= L                                      |      | 31.24   |      | mA   |

| LED output on resistance 1          | Ron1              | I <sub>O</sub> = 10mA                                          |      | 10      | 20   | Ω    |

| OFF leak current                    | lleak             | LED OFF                                                        |      |         | 10   | μА   |

| Power on RESET voltage              | VPOR              | The voltage that is canceled                                   |      | 2.5     |      | V    |

| Reset voltage                       | VRST              | UVLO voltage                                                   |      | 2.3     |      | V    |

| VREF voltage                        | VREF              | VREF=open                                                      |      | 3.2     |      | ٧    |

| Oscillator frequency                | Fosc              |                                                                |      | 1000    |      | kHz  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# Control circuit at Ta = 25°C, $V_{CC} = 3.3V$ (=VREF)

| Descriptor | O. male al | Candida                         |      | Ratings |       | Unit |

|------------|------------|---------------------------------|------|---------|-------|------|

| Parameter  | Symbol     | Conditions                      | min  | max     | Offic |      |

| H level 1  | VH1        | Input H level OUTSCT            | 2.8  |         | 3.3   | V    |

| M level 1  | VM1        | Input M level OUTSCT            | 1.2  |         | 1.7   | V    |

| L level 1  | VL1        | Input L level OUTSCT            | -0.2 |         | 0.5   | V    |

| H level 2  | VH2        | Input H level CTLSCT            | 2.3  |         | 3.3   | V    |

| L level 2  | VL2        | Input L level CTLSCT            | -0.2 |         | 0.5   | V    |

| H level 3  | VH3        | Input H level SCLK, SDATA, SDEN | 2.7  |         | 3.3   | V    |

| L level 3  | VL3        | Input L level SCLK, SDATA, SDEN | -0.2 |         | 0.6   | V    |

| H level 4  | VH4        | Input H level A0 to A3          | 2.8  |         | 3.3   | V    |

| M level 4  | VM4        | Input H level A0 to A3          | 1.35 |         | 1.8   | V    |

| L level 4  | VL4        | Input L level A0 to A3          | -0.2 |         | 0.5   | V    |

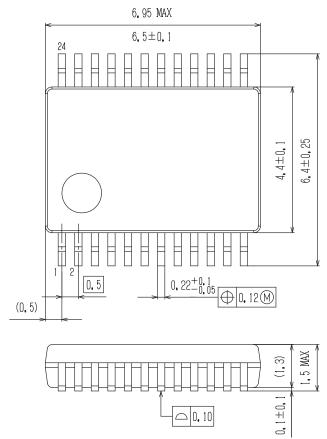

# **Package Dimensions**

unit: mm

SSOP24 (225mil) CASE 565AR ISSUE A

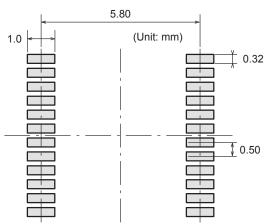

### **SOLDERING FOOTPRINT\***

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

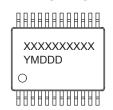

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code Y = Year

M = Month

DDD = Additional Traceability Data

<sup>\*</sup>This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present.

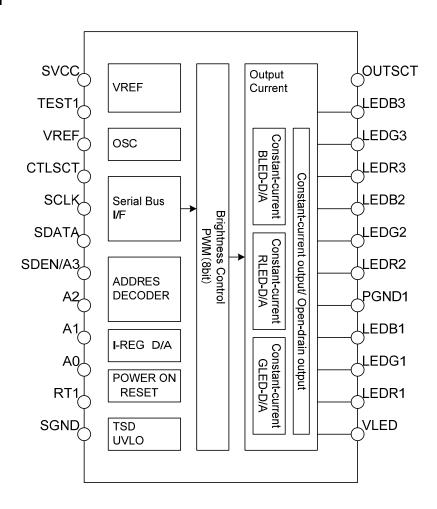

# **Block Diagram**

[Warning]: The VLED terminal becomes the terminal for protection of the LED drive output. Please be connected to the power supply same as LED drive.

When IC power supply (SVCC) and power supply of the LED or two kinds of power supply is more than it, please connect VLED to the highest potential and the power supply that it is.

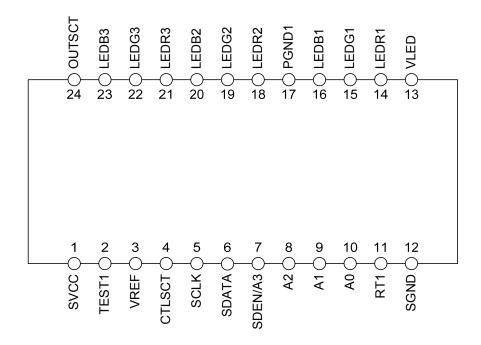

# **Pin Assignment**

# **Pin Descriptions**

| Pin No. | Pin name         | I/O | Description                                                 |

|---------|------------------|-----|-------------------------------------------------------------|

| 1       | sv <sub>CC</sub> | -   | Power supply pin                                            |

| 2       | TEST1            | 1   | Test1 pin (connected to GND)                                |

| 3       | VREF             | 0   | 5V reference output pin                                     |

| 4       | CTLSCT           | - 1 | 2-wire serial bus/3-wire serial bus selecting control pin   |

|         |                  |     | (L: 3-wire serial, H: 2-wire serial)                        |

| 5       | SCLK             | - 1 | Serial clock signal input pin                               |

| 6       | SDATA            | - 1 | Serial data signal input pin                                |

| 7       | SDEN/A3          | - 1 | Serial enable signal input pin / Slave address input pin A3 |

| 8       | A2               | 1   | Slave address input pin A2                                  |

| 9       | A1               | 1   | Slave address input pin A1                                  |

| 10      | A0               | 1   | Slave address input pin A0                                  |

| 11      | RT1              | 0   | LED current setting resistor connection pin                 |

| 12      | SGND             | -   | Analog circuit GND pin                                      |

| 13      | VLED             | 1   | Output protection pin                                       |

| 14      | LEDR1            | 0   | LEDR1 output pin                                            |

| 15      | LEDG1            | 0   | LEDG1 output pin                                            |

| 16      | LEDB1            | 0   | LEDB1 output pin                                            |

| 17      | PGND1            | 1   | GND pin dedicated for LED driver                            |

| 18      | LEDR2            | 0   | LEDR2 output pin                                            |

| 19      | LEDG2            | 0   | LEDG2 output pin                                            |

| 20      | LEDB2            | 0   | LEDB2 output pin                                            |

| 21      | LEDR3            | 0   | LEDR3 output pin                                            |

| 22      | LEDG3            | 0   | LEDG3 output pin                                            |

| 23      | LEDB3            | 0   | LEDB3 output pin                                            |

| 24      | OUTSCT           | 1   | Output type switching control pin                           |

|         |                  |     | L: Constant-current output                                  |

|         |                  |     | M:Constant output, only RGB3 is open drain output           |

|         |                  |     | H: Open drain output                                        |

**OUTSCT Settings**

| _          | LED Driver Output Pin                                      |                                                            |

|------------|------------------------------------------------------------|------------------------------------------------------------|

| OUTSCT pin | LEDR1/LEDR2                                                | LEDR3                                                      |

|            | LEDG1/ LEDG2                                               | LEDG3                                                      |

|            | LEDB1/ LEDB2                                               | LEDB3                                                      |

| L          | Constant current output                                    | Constant current output                                    |

|            | Built-in current value switching D/A (5 bits)              | Built-in current value switching D/A (5 bits)              |

|            | 0.86mA to 31.24mA, RT1=20kΩ (f=1MHz)                       | 0.86mA to 31.24mA, RT1=20kΩ (f=1MHz)                       |

| Н          | Open drain output                                          | Open drain output                                          |

|            | Current value is determined by external limiting resistor. | Current value is determined by external limiting resistor. |

|            | R <sub>ON</sub> =10Ω                                       | R <sub>ON</sub> =10Ω                                       |

| М          | Constant current output                                    | Open drain output                                          |

|            | Built-in current value switching D/A (5 bits)              | Current value is determined by external limiting resistor. |

|            | 0.86mA to 31.24mA, RT1=20kΩ (f=1MHz)                       | R <sub>ON</sub> =10Ω                                       |

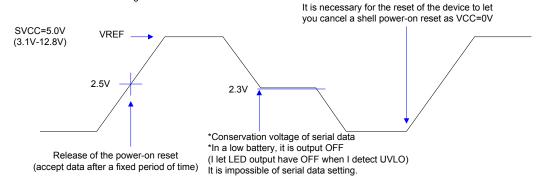

#### **Power on RESET Settings**

It has power-on reset circuit built-in, and, at the time of power activation, the air resister data of the IC is reset.

It prevents malfunction of the LED lighting by letting you reset it.

When voltage rises from state of SVCC=0V, the power-on reset becomes effective.

Please start to reboot it after making SVCC=0V.

When you transmit data after a release of the power-on reset, please transmit it after being able to open interval more than 100usec.

### **Pin Functions**

| Pin No. | Pin Name         | Pin function                                                                                                                                                                                    | Equivalent Circuit                                |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1       | sv <sub>CC</sub> | Power supply pin                                                                                                                                                                                |                                                   |

| 2       | TEST1            | Test1 pin This pin must always be connected to GND.                                                                                                                                             | TEST1  10kΩ  60kΩ  77  77  77  77  77  77  77  77 |

| 3       | VREF             | Reference output pin(5V)                                                                                                                                                                        |                                                   |

| 4       | CTLSCT           | Serial bus communication setting pin When set to low: The 3-wire serial bus signals are set as the input signals. When set to high: The 2-wire serial bus signals are set as the input signals. | CTLSCT 10kΩ                                       |

| 5  | SCLK     | Serial clock signal input pin                 |                                       |

|----|----------|-----------------------------------------------|---------------------------------------|

|    |          | • • •                                         | SCLK                                  |

| 6  | SDATA    | Serial data signal input pin                  | SDATA                                 |

| 7  | SDEN/ A3 | Serial enable signal input pin/               | SDEN/A3                               |

|    |          | Slave address setting pin A3                  |                                       |

|    |          |                                               | <del>\</del> }                        |

|    |          |                                               |                                       |

|    |          |                                               |                                       |

|    |          |                                               | <i>''' '''</i>                        |

| 8  | A2       | Slave address setting pin A2                  |                                       |

|    |          |                                               | VREF                                  |

| 9  | A1       | Slave address setting pin A1                  |                                       |

| 10 | A0       | Slave address setting pin A0                  | 115kΩ ≰ 太                             |

|    |          |                                               | A0<br>A1 sto                          |

|    |          |                                               | $A1 \atop A2 \atop \uparrow $         |

|    |          |                                               | A3 ()                                 |

|    |          |                                               | 5kΩ 🔰 🔲                               |

|    |          |                                               | <u> </u>                              |

|    |          |                                               | 100kΩ ≸ ★                             |

|    |          |                                               |                                       |

|    |          |                                               | /// /// /// ///                       |

| 44 | DT4      | Deference current actions are inter-          |                                       |

| 11 | RT1      | Reference current setting resistor            | VREF                                  |

|    |          | connection pin.                               |                                       |

|    |          | By connecting the external register between   |                                       |

|    |          | this pin and GND, the reference current is    | T                                     |

|    |          | generated. The pin voltage is approximately   | RT1 500Ω ≸                            |

|    |          | 1.22V. By changing the current level, it is   |                                       |

|    |          | possible to change the oscillator frequency   | 500Ω≨ Τ                               |

|    |          | and LED driver current value (in the          | BGR                                   |

|    |          | constant-current mode).                       | =1.22V                                |

|    |          | constant current mode).                       |                                       |

|    |          |                                               | <i>'''</i>                            |

| 12 | SGND     | GND pin                                       |                                       |

| 12 | SGND     | GND pin                                       |                                       |

| 13 | VLED     | Outrat and attended                           |                                       |

| 13 | VLED     | Output protection pin                         |                                       |

| 14 | LEDR1    | LEDR1 output pin                              |                                       |

| 15 | LEDG1    | LEDG1 output pin                              | VLED                                  |

| 16 | LEDB1    | LEDB1 output pin                              |                                       |

| 18 | LEDR2    | LEDR2 output pin                              | LEDO ᄎ                                |

| 19 | LEDG2    | LEDG2 output pin                              |                                       |

| 20 | LEDB2    | LEDB2 output pin                              | $\cup$                                |

|    |          |                                               | ├──────────────────────────────────── |

| 21 | LEDR3    | LEDR3 output pin                              | │                                     |

| 22 | LEDG3    | LEDG3 output pin                              |                                       |

| 23 | LEDB3    | LEDB3 output pin                              |                                       |

|    |          | If these pins are not going to be used, they  | गी गी                                 |

|    |          | must always be connected to GND.              |                                       |

| 17 | PGND1    | GND pin dedicate for LED output               |                                       |

| 24 | OUTSCT   | LED driver output type setting pin            | \/D5=                                 |

|    |          | When set to low: Constant-current output is   | VREF                                  |

|    |          | set for the LED driver.                       |                                       |

|    |          |                                               | 115kΩ ≱                               |

|    |          | When set to high: Open drain output is set    | OUTCOT FLO S                          |

|    |          | for the LED driver.                           | OUTSCT 5kΩ \$                         |

|    |          | When set to middle: Constant-current output   |                                       |

|    |          | is set for the LED driver. However, open      | 5kΩ 🔰 💄                               |

|    |          | drain output is set for the only LED3 driver. |                                       |

|    |          |                                               | 100kΩ ≩                               |

|    |          |                                               |                                       |

|    |          |                                               |                                       |

|    |          |                                               |                                       |

### **Serial Bus Communication Specifications**

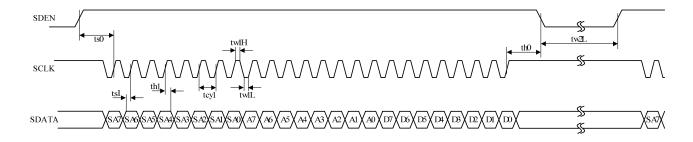

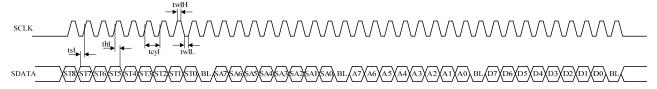

### 1) Serial bus transfer timing conditions

| Parameter       | Symbol | Conditions                                    | Min. | Тур. | Max. | Unit |

|-----------------|--------|-----------------------------------------------|------|------|------|------|

| Cycle time      | tcy1   | SCLK clock period                             | 200  | -    | -    | ns   |

| Data setup time | ts0    | SDEN setup time relative to the rise of SCLK  | 90   | -    | -    | ns   |

|                 | ts1    | SDATA setup time relative to the rise of SCLK | 60   | -    | -    | ns   |

| Data hold time  | th0    | SDEN hold time relative to the fall of SCLK   | 200  | -    | -    | ns   |

|                 | th1    | SDATA hold time relative to the fall of SCLK  | 60   | -    | -    | ns   |

| Pulse width     | tw1L   | Low period pulse width of SCLK                | 90   | -    | -    | ns   |

|                 | tw1H   | High period pulse width of SCLK               | 90   | -    | -    | ns   |

|                 | tw2L   | Low period pulse width of SDEN                | 1    | -    | -    | μS   |

#### 2) 3-wire serial bus transfer formats

LV5237JA receives the command by communication format by 3 line type serial communication of SCLK, SDATA, and SDEN.

#### When SCLK stops in "L" level

#### When SCLK stops in "H" level

Data length : 24bits

Clock frequency: 5MHz or less

When 24 SCLK clock signals have been input during the high period of SDEN, the SDATA is taken in at the rising edge of SCLK.

Note: If the number of SCLK clock signals during the high period of SDEN is 23 or less, SDATA is not taken in. If it is 25 or more, the register address is automatically incremented every time 1byte is taken in.

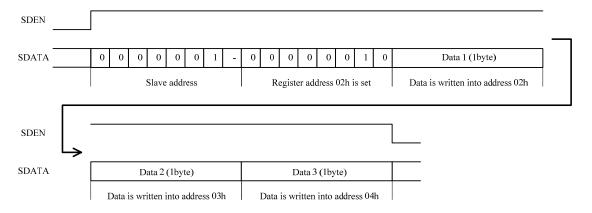

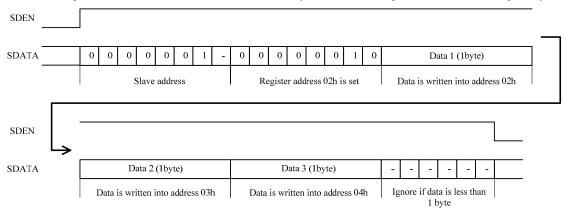

#### Data organization

The slave address is assigned by the first byte, and the register address on the serial map is specified by the next byte. The third byte transfers the data to the address specified by the register address that was written by the second byte and if the data subsequently continues even after this, the register address is automatically incremented for the fourth and subsequent bytes. As a result, it is possible to send the data continuously from the specified addresses. Data of less than one byte is ignored. However, when the address reaches 0fh, the next byte to be transferred becomes 00h.

Serial data transfer example (slave address=0000 001-)

When I set register address 02h and write in data (the smallest data length)

When I set register address 02h and write in data for 3 bytes

When I set register address 02h and write in data for 3 byte, and following data is less than a signal byte

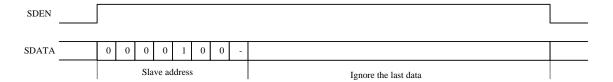

When slave address does not accord

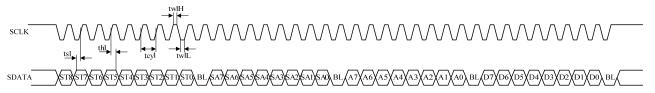

#### 3) 2-wire serial bus transfer formats

LV5237JA receives the command by communication format by 2 line type serial communication of SCLK, SDATA.

### When SCLK stops in "L" level

#### When SCLK stops in "H" level

Data length : 37bits

Start condition ("111111111") + BLANK ("0") + Slave address (8bit) + BLANK + ("0") +

Resister address (8bit) + BLANK ("0") + Data (8bit) + BLANK ("0")

Clock frequency: 5MHz or less

After start detection, it takes SDATA in the timing when the 27th clock track of SCLK stands up when sign according to communication format is input into SCLK and SDATA.

Note: When SCLK is less than 27th clock track, and BLANK is different from communication format such as "1", after start detection, do not take in SDATA.

When SCLK is higher than 28th clock track, start detection is confirmed, or it is automatic, and register address is incremented every 1byte (8bit) + BLANK ("0") unless BLANL is "1".

#### Data organization

| bit       | ST8 | ST7 | ST6 | ST5   | ST4  | ST3   | ST2 | STI | STO | BL                    | SA7 | SA6 | SA5 | SA4   | SA3 | SA2  | SAI | SAO | BL                    | A7 | A6 | A5 | A4     | A3    | A2    | A1 | A0 | BL                    | D7 | D6 | D5 | D4 | D3  | D2 | Dl | D0 | BL                    |

|-----------|-----|-----|-----|-------|------|-------|-----|-----|-----|-----------------------|-----|-----|-----|-------|-----|------|-----|-----|-----------------------|----|----|----|--------|-------|-------|----|----|-----------------------|----|----|----|----|-----|----|----|----|-----------------------|

| SDATA     | 1   | 1   | 1   | 1     | 1    | 1     | 1   | 1   | 1   | 0                     | 0   | 0   |     |       |     |      |     | -   | 0                     |    |    |    |        |       |       |    |    | 0                     |    |    |    |    |     |    |    |    | 0                     |

| Parameter |     |     |     | Start | cond | ition |     |     |     | B<br>L<br>A<br>N<br>K |     |     |     | Slave | add | ress |     |     | B<br>L<br>A<br>N<br>K |    |    | R  | legist | er ad | dress |    |    | B<br>L<br>A<br>N<br>K |    |    |    | D  | ata |    |    |    | B<br>L<br>A<br>N<br>K |

Even if SCLK and SDATA are state such as among standby or serial data inward correspondences, "111111111" start assumption and BLANK"0" start the uptake atomic act of new serial data after detection (start detection) was considered to be it.

After start detection, the first single byte (8bit) is assigned to slave address, and a write store of the slave address completes it in BLANK"0".

The next single byte appoints register address in the serial manufacturing auto protocol, and a write of the register address is completed in BLANK"0".

The third byte performs a data transfer to the address which it appointed in the register address which it wrote in at the second byte and it complete data transfer in BLANK"0" and write in it. When data continues after this, register address is automatically incremented after the fourth byte and a data transfer is completed each time and, in BLANK"0", writes in it.

Data Forward continuous from designated register address is enabled, but, as for the redirecting address of the next byte, it is in this way with for "00h" when register address becomes "0fh".

In addition, when serial data uptake BLANK is "1", including slave address selection and register address assignment, the single byte data just before it is ignored without being written in, and the subsequent data is ignored until it is detected a start.

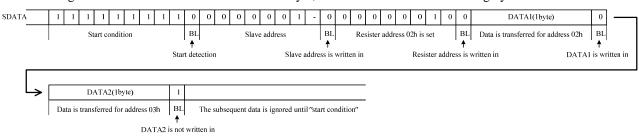

Serial data transfer example (slave address=0000 001-)

#### When I set register address 02h and write in data (the smallest data length)

#### When I set register address 02h and write in data for 3 bytes

### When I set register address 02h and write in data for 1 byte, and BLANK after the following byte in the case of "1"

#### When I set register address 02h, but BLANK after the byte in the case of "1"

#### When slave address does not accord

# SDATA continues more than 10bit; and in the case of 1 "" (start detection of this case)

#### Slave address condition

|               |     | SLAVE ADDRESS |     |     |     |     |     |     |

|---------------|-----|---------------|-----|-----|-----|-----|-----|-----|

|               | SA7 | SA6           | SA5 | SA4 | SA3 | SA2 | SA1 | SA0 |

| resister name | -   |               |     | A3  | A2  | A1  | A0  | -   |

| default       | 0   | 0             | 0   | 0   | 0   | 0   | 0   | _   |

|          | Te     | rminal F | PIN |        |

|----------|--------|----------|-----|--------|

|          | A3     | A2       | A1  | A0     |

|          | L      | L        | L   | L      |

|          | L      | L        | L   | М      |

|          | L      | L        | L   | Н      |

|          | L      | L        | M   | L      |

|          | L      | L        | М   | M      |

|          | L      | L        | М   | Н      |

|          | L      | L        | H   | L      |

|          | L      | L        | Н   | M      |

|          | L      | L        | H   | H      |

|          | L      | M        | L   | L      |

|          | L      | M        | L   | M      |

|          | L      | M        | L   | Н      |

|          | L      | M        | M   | L      |

|          | L      | M        | M   | M      |

|          | L      | M        | M   | Н      |

|          | L      | M        | Н   | L      |

|          | L      | M        | Н   | M      |

|          | L      | M        | H   | Н      |

|          | L      | Н        | L   | L      |

|          |        |          |     | M      |

|          | L<br>L | Н        | L   |        |

|          | L      | H        |     | H<br>L |

|          |        | H        | M   |        |

|          | L .    | H        | M   | M      |

|          | L .    | H        | M   | H      |

|          | L      | Н        | Н   | L      |

|          | L .    | Н        | H   | M      |

|          | L      | H        | H   | H      |

|          | M      | L        | L   | L      |

|          | M      | L        | L   | M      |

|          | M      | L        | L   | H      |

|          | M      | L        | M   | L      |

|          | M      | L        | M   | M      |

|          | M      | L        | M   | H      |

|          | M      | L        | H   | L      |

|          | M      | L        | H   | M      |

|          | M      | L        | H   | H      |

|          | М      | M        | L   | L      |

|          | M      | M        | L   | M      |

|          | M      | M        | L   | H      |

| $\vdash$ | M      | M        | M   | L      |

|          | M      | M        | M   | M      |

|          | М      | M        | M   | H      |

|          | М      | M        | Н   | L      |

|          | М      | M        | Н   | M      |

|          | М      | M        | Н   | Н      |

|          | М      | Н        | L   | L      |

|          | М      | Н        | L   | M      |

|          | М      | Н        | L   | Н      |

|          | M      | Н        | M   | L      |

| 0.47 | 040 | 0.4.5 | 044 | 040 | 040 | 0.1.1 | 040 | I  |

|------|-----|-------|-----|-----|-----|-------|-----|----|

| SA7  | SA6 | SA5   | SA4 | SA3 | SA2 | SA1   | SA0 |    |

| 0    | 0   | 0     | 0   | 0   | 0   | 0     | -   | 1  |

| 0    | 0   | 0     | 0   | 0   | 0   | 1     | -   | 2  |

| 0    | 0   | 0     | 0   | 0   | 1   | 0     | -   | 3  |

| 0    | 0   | 0     | 0   | 0   | 1   | 1     | -   | 4  |

| 0    | 0   | 0     | 0   | 1   | 0   | 0     | -   | 5  |

| 0    | 0   | 0     | 0   | 1   | 0   | 1     | -   | 6  |

| 0    | 0   | 0     | 0   | 1   | 1   | 0     | -   | 7  |

| 0    | 0   | 0     | 0   | 1   | 1   | 1     | -   | 8  |

| 0    | 0   | 0     | 1   | 0   | 0   | 0     | -   | 9  |

| 0    | 0   | 0     | 1   | 0   | 0   | 1     | -   | 10 |

| 0    | 0   | 0     | 1   | 0   | 1   | 0     | -   | 11 |

| 0    | 0   | 0     | 1   | 0   | 1   | 1     | -   | 12 |

| 0    | 0   | 0     | 1   | 1   | 0   | 0     | -   | 13 |

| 0    | 0   | 0     | 1   | 1   | 0   | 1     | -   | 14 |

| 0    | 0   | 0     | 1   | 1   | 1   | 0     | -   | 15 |

| 0    | 0   | 0     | 1   | 1   | 1   | 1     | -   | 16 |

| 0    | 0   | 1     | 0   | 0   | 0   | 0     | -   | 17 |

| 0    | 0   | 1     | 0   | 0   | 0   | 1     | -   | 18 |

| 0    | 0   | 1     | 0   | 0   | 1   | 0     | -   | 19 |

| 0    | 0   | 1     | 0   | 0   | 1   | 1     | -   | 20 |

| 0    | 0   | 1     | 0   | 1   | 0   | 0     | -   | 21 |

| 0    | 0   | 1     | 0   | 1   | 0   | 1     | -   | 22 |

| 0    | 0   | 1     | 0   | 1   | 1   | 0     | -   | 23 |

| 0    | 0   | 1     | 0   | 1   | 1   | 1     | -   | 24 |

| 0    | 0   | 1     | 1   | 0   | 0   | 0     | -   | 25 |

| 0    | 0   | 1     | 1   | 0   | 0   | 1     | -   | 26 |

| 0    | 0   | 1     | 1   | 0   | 1   | 0     | -   | 27 |

| 0    | 0   | 1     | 1   | 0   | 1   | 1     | -   | 28 |

| 0    | 0   | 1     | 1   | 1   | 0   | 0     | -   | 29 |

| 0    | 0   | 1     | 1   | 1   | 0   | 1     | -   | 30 |

| 0    | 0   | 1     | 1   | 1   | 1   | 0     | -   | 31 |

| 0    | 0   | 1     | 1   | 1   | 1   | 1     |     | 32 |

| 0    | 1   | 0     | 0   | 0   | 0   | 0     |     | 33 |

| 0    | 1   | 0     | 0   | 0   | 0   | 1     |     | 34 |

| 0    | 1   | 0     | 0   | 0   | 1   | 0     |     | 35 |

| 0    | 1   | 0     | 0   | 0   | 1   | 1     |     | 36 |

| 0    | 1   | 0     | 0   | 1   | 0   | 0     |     | 37 |

| 0    | 1   | 0     | 0   | 1   | 0   | 1     |     | 38 |

| 0    | 1   | 0     | 0   | 1   | 1   | 0     |     | 39 |

| 0    | 1   | 0     | 0   | 1   | 1   | 1     |     | 40 |

| 0    | 1   | 0     | 1   | 0   | 0   | 0     |     | 41 |

| 0    | 1   | 0     | 1   | 0   | 0   | 1     |     | 42 |

| 0    | 1   | 0     | 1   | 0   | 1   | 0     |     | 43 |

| 0    | 1   | 0     | 1   | 0   | 1   | 1     |     | 44 |

| 0    | 1   | 0     | 1   | 1   | 0   | 0     |     | 45 |

| 0    | 1   | 0     | 1   | 1   | 0   | 1     |     |    |

|      |     |       | 1   |     |     |       |     | 46 |

| 0    | 1   | 0     | 1   | 1   | 1   | 0     |     | 47 |

| 0    | 1   | 0     |     |     |     | 1     |     | 48 |

| 0    | 1   | 1     | 0   | 0   | 0   | 0     | -   | 49 |

:LV5237

| Te | rminal F | PIN |    |

|----|----------|-----|----|

| А3 | A2       | A1  | A0 |

| М  | Н        | М   | М  |

| М  | Н        | М   | Н  |

| М  | Н        | Η   | L  |

| М  | Н        | Η   | М  |

| М  | Н        | Н   | Н  |

| Н  | L        | L   | L  |

| Н  | L        | L   | М  |

| Н  | L        | L   | Н  |

| Н  | L        | М   | L  |

| Н  | L        | М   | М  |

| Н  | L        | М   | Н  |

| Н  | L        | Н   | L  |

| Н  | L        | Η   | М  |

| Н  | L        | Н   | Н  |

| Н  | М        | L   | L  |

| Н  | М        | L   | М  |

| Н  | М        | L   | Н  |

| Н  | М        | М   | L  |

| Н  | М        | М   | М  |

| Н  | М        | М   | Н  |

| Н  | М        | Н   | L  |

| Н  | М        | Н   | М  |

| Н  | М        | Н   | Н  |

| Н  | Н        | L   | L  |

| Н  | Н        | L   | М  |

| Н  | Н        | L   | Н  |

| Н  | Н        | М   | L  |

| Н  | Н        | М   | М  |

| Н  | Н        | М   | Н  |

| Н  | Н        | Н   | L  |

| Н  | Н        | Н   | М  |

| Н  | Н        | Н   | Н  |

| 0         1         1         0         0         0         1         -           0         1         1         0         0         1         0         -           0         1         1         0         0         1         1         -           0         1         1         0         1         0         0         -           0         1         1         0         1         1         0         -           0         1         1         0         1         1         0         -           0         1         1         0         0         0         -         -           0         1         1         1         0         0         0         -           0         1         1         1         0         0         0         -           0         1         1         1         1         0         1         -           0         1         1         1         1         1         1         1         -           0         1         1         1         1         1         1                                                                         | SA7 | SA6 | SA5 | SA4 | SA3 | SA2 | SA1 | SA0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0         1         1         0         0         1         1         -           0         1         1         0         1         0         0         -           0         1         1         0         1         0         1         -         0         1         -         0         1         -         0         0         0         -         0         0         0         -         0         0         0         -         0         0         0         -         0         0         0         -         0         0         0         0         -         0         0         0         0         -         0         1         1         1         0         0         0         -         0         1         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1 | 0   | 1   | 1   | 0   | 0   | 0   | 1   | -   |

| 0         1         1         0         1         0         0         -           0         1         1         0         1         0         1         -           0         1         1         0         1         1         0         -           0         1         1         0         0         0         -           0         1         1         1         0         0         0         -           0         1         1         1         0         0         1         -           0         1         1         1         0         0         1         -           0         1         1         1         0         0         1         -           0         1         1         1         1         0         0         -           0         1         1         1         1         1         0         0         -           0         1         1         1         1         1         1         1         1         0         -           1         1         0         0         0                                                                         | 0   | 1   | 1   | 0   | 0   | 1   | 0   | -   |

| 0         1         1         0         1         0         1         -           0         1         1         0         1         1         0         -           0         1         1         1         0         0         0         -           0         1         1         1         0         0         0         -           0         1         1         1         0         0         1         -           0         1         1         1         0         1         1         -           0         1         1         1         0         1         1         -           0         1         1         1         1         0         0         -           0         1         1         1         1         1         0         0         -           0         1         1         1         1         1         1         1         1         -           0         1         1         1         1         1         1         1         -         -         -         -         1         1                                                                 | 0   | 1   | 1   | 0   | 0   | 1   | 1   | -   |

| 0         1         1         0         1         1         0         -           0         1         1         0         1         1         1         -           0         1         1         1         0         0         0         -           0         1         1         1         0         0         0         -           0         1         1         1         0         1         1         -           0         1         1         1         0         1         1         -           0         1         1         1         1         0         0         -           0         1         1         1         1         1         0         0         -           0         1         1         1         1         1         1         1         -         -           0         1         1         1         1         1         1         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                         | 0   | 1   | 1   | 0   | 1   | 0   | 0   | -   |

| 0         1         1         0         1         1         1         -           0         1         1         1         0         0         0         -           0         1         1         1         0         0         1         -           0         1         1         1         0         1         1         -           0         1         1         1         1         0         1         1         -           0         1         1         1         1         0         0         -         -           0         1         1         1         1         1         0         0         -           0         1         1         1         1         1         1         1         -         -           0         1         1         1         1         1         1         1         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                 | 0   | 1   | 1   | 0   | 1   | 0   | 1   | -   |

| 0         1         1         1         0         0         0         -           0         1         1         1         0         0         1         -           0         1         1         1         0         1         0         -           0         1         1         1         0         1         1         -           0         1         1         1         1         1         0         0         -           0         1         1         1         1         1         1         1         -         -           0         1         1         1         1         1         1         1         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                 | 0   | 1   | 1   | 0   | 1   | 1   | 0   | -   |

| 0         1         1         1         0         0         1         -           0         1         1         1         0         1         0         -           0         1         1         1         0         1         1         -           0         1         1         1         1         0         0         -           0         1         1         1         1         1         0         0         -           0         1         1         1         1         1         1         1         1         -         -           0         1         1         1         1         1         1         1         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                 | 0   | 1   | 1   | 0   | 1   | 1   | 1   | -   |

| 0         1         1         1         0         1         0         -           0         1         1         1         0         1         1         -           0         1         1         1         1         0         0         -           0         1         1         1         1         0         1         -           0         1         1         1         1         1         1         1         -           0         1         1         1         1         1         1         1         -         -           0         1         1         1         1         1         1         1         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                 | 0   | 1   | 1   | 1   | 0   | 0   | 0   | -   |

| 0         1         1         1         0         1         1         -           0         1         1         1         1         0         0         -           0         1         1         1         1         0         1         -           0         1         1         1         1         1         0         -           0         1         1         1         1         1         1         1         -           0         1         1         1         1         1         1         1         -         -           1         1         0         0         0         0         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                 | 0   | 1   | 1   | 1   | 0   | 0   | 1   | -   |

| 0         1         1         1         1         0         0         -           0         1         1         1         1         0         1         -           0         1         1         1         1         1         1         0         -           0         1         1         1         1         1         1         1         -         -           1         1         0         0         0         0         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                 | 0   | 1   | 1   | 1   | 0   | 1   | 0   | -   |

| 0         1         1         1         1         0         1         -           0         1         1         1         1         1         0         -           0         1         1         1         1         1         1         1         -           1         1         0         0         0         0         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         | 0   | 1   | 1   | 1   | 0   | 1   | 1   | -   |

| 0         1         1         1         1         0         -           0         1         1         1         1         1         1         1         -           1         1         0         0         0         0         0         -         -           1         1         0         0         0         0         1         -         -           1         1         0         0         0         1         0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                 | 0   | 1   | 1   | 1   | 1   | 0   | 0   | -   |

| 0         1         1         1         1         1         -           1         1         0         0         0         0         0         -           1         1         0         0         0         0         1         -           1         1         0         0         0         1         0         -           1         1         0         0         1         0         0         -           1         1         0         0         1         0         0         -           1         1         0         0         1         1         0         -           1         1         0         0         1         1         0         -           1         1         0         0         1         1         0         -           1         1         0         1         1         1         1         -           1         1         0         1         1         1         0         0         1           1         1         0         1         0         1         1         1                                                                         | 0   | 1   | 1   | 1   | 1   | 0   | 1   | -   |

| 1       1       0       0       0       0       0       -         1       1       0       0       0       0       1       -         1       1       0       0       0       1       0       -         1       1       0       0       0       1       1       -         1       1       0       0       1       0       0       -         1       1       0       0       1       0       1       -         1       1       0       0       1       1       0       -         1       1       0       0       1       1       1       -         1       1       0       1       1       1       1       -         1       1       0       1       0       0       0       1       1       -         1       1       0       1       0       0       0       1       1       1       0       1       1       1       0       1       1       1       1       1       1       1       0       1       1       1                                                                                                                                                                         | 0   | 1   | 1   | 1   | 1   | 1   | 0   | -   |

| 1       1       0       0       0       0       1       -         1       1       0       0       0       1       0       -         1       1       0       0       0       1       1       -         1       1       0       0       1       0       0       -         1       1       0       0       1       0       1       -         1       1       0       0       1       1       0       -         1       1       0       0       1       1       1       -         1       1       0       1       0       0       0       0       -         1       1       0       1       0       0       0       0       1       1       -         1       1       0       1       0       0       0       0       1       0       0       0       1       1       0       1       1       0       0       1       1       0       1       1       0       0       1       1       1       0       0       1       1                                                                                                                                                                   | 0   | 1   | 1   | 1   | 1   | 1   | 1   | -   |

| 1       1       0       0       0       1       0       -         1       1       0       0       0       1       1       -         1       1       0       0       1       0       0       -         1       1       0       0       1       0       1       -         1       1       0       0       1       1       0       -         1       1       0       0       1       1       1       -         1       1       0       1       0       0       0       0       0       0       0       1       1       1       -       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       <                                                                                                                                         | 1   | 1   | 0   | 0   | 0   | 0   | 0   | -   |

| 1       1       0       0       0       1       1       -         1       1       0       0       1       0       0       -         1       1       0       0       1       0       1       -         1       1       0       0       1       1       0       -         1       1       0       0       1       1       1       -         1       1       0       1       0       0       0       0         1       1       0       1       0       0       1       1       0         1       1       0       1       0       1       0       1       1       1       0       0       0       0       0       0       0       0       0       0       0       1       1       0       1       1       0       1       1       0       0       0       0       0       0       0       0       0       1       1       0       0       0       0       0       0       1       1       0       0       0       0       0       0                                                                                                                                                       | 1   | 1   | 0   | 0   | 0   | 0   | 1   | -   |

| 1     1     0     0     1     0     0     -       1     1     0     0     1     0     1     -       1     1     0     0     1     1     0     -       1     1     0     0     1     1     1     -       1     1     0     1     0     0     0     0       1     1     0     1     0     0     1     0     1       1     1     0     1     0     1     0     1     1     1       1     1     0     1     1     0     0     1     1     0     1       1     1     0     1     1     1     0     1     1     1     0       1     1     0     1     1     1     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1   | 1   | 0   | 0   | 0   | 1   | 0   | -   |

| 1       1       0       0       1       0       1       -         1       1       0       0       1       1       0       -         1       1       0       0       1       1       1       -         1       1       0       1       0       0       0       0         1       1       0       1       0       0       1       0       1         1       1       0       1       0       1       0       1       1       1       0       0       1       1       1       0       1       1       1       0       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1       1       1       0       1 <td< td=""><td>1</td><td>1</td><td>0</td><td>0</td><td>0</td><td>1</td><td>1</td><td>-</td></td<>                                         | 1   | 1   | 0   | 0   | 0   | 1   | 1   | -   |

| 1     1     0     0     1     1     0     -       1     1     0     0     1     1     1     -       1     1     0     1     0     0     0       1     1     0     1     0     0     1       1     1     0     1     0     1     0       1     1     0     1     0     1     1       1     1     0     1     1     0     0       1     1     0     1     1     0     1       1     1     0     1     1     1     0       1     1     0     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | 1   | 0   | 0   | 1   | 0   | 0   | -   |

| 1     1     0     0     1     1     1     -       1     1     0     1     0     0     0       1     1     0     1     0     0     1       1     1     0     1     0     1     0       1     1     0     1     0     1     1       1     1     0     1     1     0     0       1     1     0     1     1     0     1       1     1     0     1     1     1     0       1     1     0     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1   | 1   | 0   | 0   | 1   | 0   | 1   | -   |

| 1     1     0     1     0     0     0       1     1     0     1     0     0     1       1     1     0     1     0     1     0       1     1     0     1     0     1     1       1     1     0     1     1     0     0       1     1     0     1     1     0     1       1     1     0     1     1     1     0       1     1     0     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1   | 1   | 0   | 0   | 1   | 1   | 0   | -   |

| 1     1     0     1     0     0     1       1     1     0     1     0     1     0       1     1     0     1     0     1     1       1     1     0     1     1     0     0       1     1     0     1     1     0     1       1     1     0     1     1     1     0       1     1     0     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | 1   | 0   | 0   | 1   | 1   | 1   | -   |

| 1     1     0     1     0     1     0       1     1     0     1     0     1     1       1     1     0     1     1     0     0       1     1     0     1     1     0     1       1     1     0     1     1     1     0       1     1     0     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1   | 1   | 0   | 1   | 0   | 0   | 0   |     |

| 1     1     0     1     0     1     1       1     1     0     1     1     0     0       1     1     0     1     1     0     1       1     1     0     1     1     1     0       1     1     0     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1   | 1   | 0   | 1   | 0   | 0   | 1   |     |

| 1     1     0     1     1     0     0       1     1     0     1     1     0     1       1     1     0     1     1     1     0       1     1     0     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1   | 1   | 0   | 1   | 0   | 1   | 0   |     |

| 1     1     0     1     1     0     1       1     1     0     1     1     1     0       1     1     0     1     1     1     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | 1   | 0   | 1   | 0   | 1   | 1   |     |

| 1 1 0 1 1 0<br>1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1   | 1   | 0   | 1   | 1   | 0   | 0   |     |

| 1 1 0 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | 1   | 0   | 1   | 1   | 0   | 1   |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1   | 1   | 0   | 1   | 1   | 1   | 0   |     |